MSc thesis project proposal

[2024] Digital VLSI Accelerator for Ultra-Low-Latency Event-Driven Eye-Tracking

Introduction

This project is about developing a Digital VLSI Accelerator specifically designed to enhance the efficiency and accuracy of eye-tracking systems. The core innovation lies in leveraging ultra-low-latency event-driven mechanisms in real-time tracking applications.

The primary aim of this project is to design and implement a VLSI system that significantly reduces the latency in eye-tracking devices. This system will be capable of processing high-volume data streams efficiently, ensuring swift and accurate eye movement tracking.

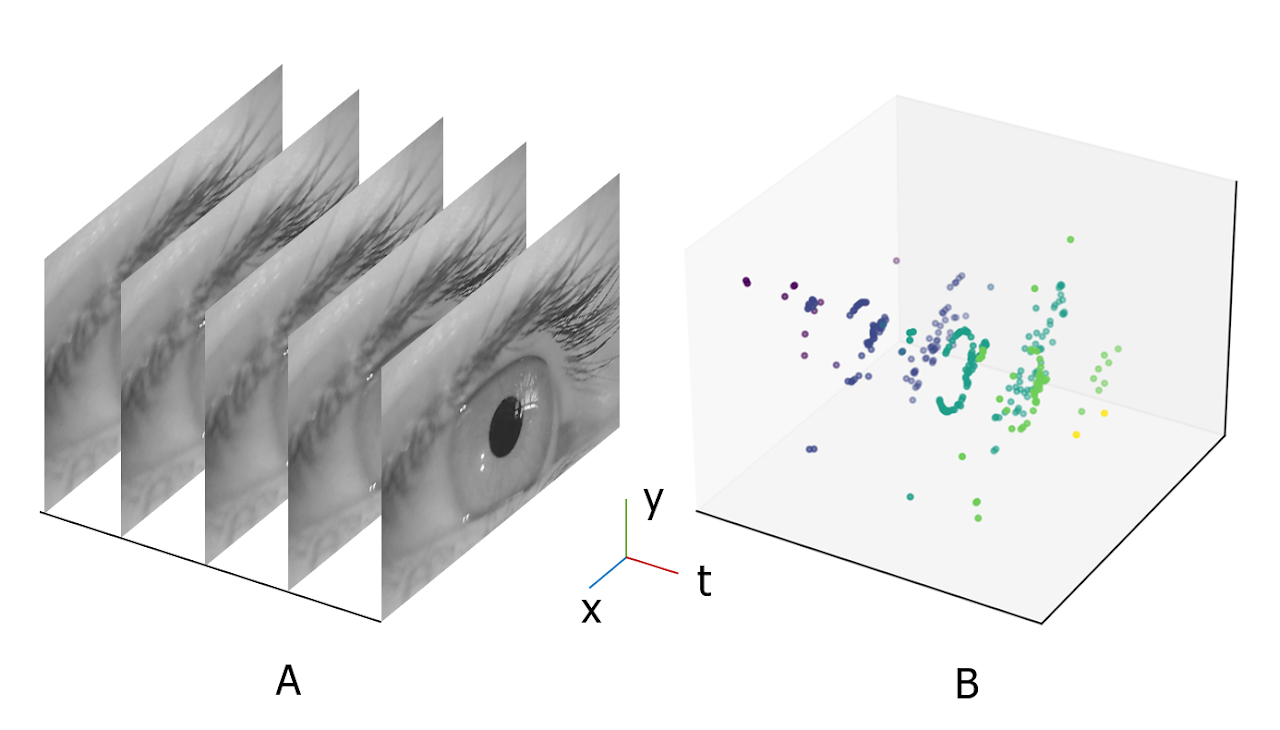

Importance of Event-Cameras in Eye Tracking

Event cameras represent a pivotal technology in this context. Unlike traditional cameras, event cameras capture pixel-level changes in the scene, resulting in high temporal resolution and sparse data output. This characteristic is particularly beneficial for eye-tracking, as it captures minute and rapid eye movements with greater precision. Furthermore, the sparse data pattern generated by event cameras reduces computational load, making it ideal for efficient hardware implementation.

Potential Impact and Applications

The successful development of this accelerator has far-reaching implications. It can revolutionize how eye-tracking is used in various fields, such as virtual/augmented reality, medical diagnostics, and human-computer interaction.

Opportunity for Further Research

This Master's thesis project can potentially evolve into a Ph.D. project. It offers an excellent opportunity for students interested in cutting-edge research and real-world application of advanced digital systems.

Want to Know More?

Contact me (chang.gao at tudelft.nl) to book a short meeting. You can also read this paper from Stanford: https://arxiv.org/abs/2004.03577

Assignment

The project will involve:

- Research and Analysis: Conducting a thorough study of current VLSI technologies and event-camera systems to identify areas of potential improvement.

- Design and Development: Designing the VLSI accelerator architecture tailored for ultra-low-latency processing. This will include developing algorithms that optimally utilize the sparse data patterns from event cameras.

- Testing and Optimization: Implementing the design on a suitable hardware platform and rigorously testing for performance metrics like latency, accuracy, and power consumption.

Requirements

An ideal candidate should have knowledge and skills in:

- VLSI fundamentals (front-end design and verification, capable of doing power analysis)

- SystemVerilog/Verilog

- Deep Neural Networks (experience in Python & PyTorch)

Contact

dr. Chang Gao

Electronic Circuits and Architectures Group

Department of Microelectronics

Last modified: 2023-11-12